3A, Single Cell Li-Ion DC/DC Switching Charger with I<sup>2</sup>C Control, USB Detection and OTG, JEITA Compliant, Power Path Management

## **General Description**

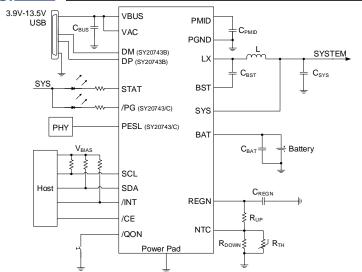

The SY20743/B/C is a fully-integrated switching battery charger with system power path management device for single cell Li-Ion and Li-polymer batteries in a wide range of tablets and other portable devices. The low on-resistance of the main switch, synchronous rectifier switches and BATFET helps improving the switching conversion efficiency, shortening the charge cycle, and prolonging the battery life. The integrated I<sup>2</sup>C serial interface enables the host to configure the device for different applications.

The device supports a wide range of input sources, including standard USB host ports, USB charging ports and USB compliant adjustable high voltage adapters. The SY20743/C takes the result from a detection circuit in the system, such as a USB PHY device, while the SY20743B takes the detection result from the internal USB port identification circuit thru DP/DM to enable BC1.2 compliance. The SY20743/B/C is compliant with USB 2.0 and USB 3.0 power specification with input current and voltage regulation. The SY20743/B/C meets the USB On-the-go operation power rating specification by supplying 5.15V (programmable) on BUS rail with a programmable current limit of up to 1.2A.

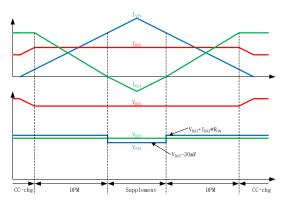

The integrated power path management provides the system power supply and regulates the system voltage above 3.5V minimum system voltage (programmable) with high priority, even when battery voltage is low. This architecture allows automatically reducing the charging current when the system load demands more current. Furthermore, if the system load demand still cannot be met, the power path control logic enables the BATFET to enter supplement mode, where the battery and the adapter are supplying power to the system at the same time.

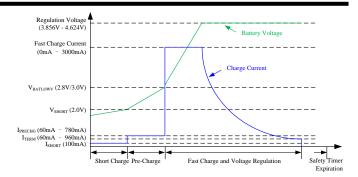

The SY20743/B/C can automatically start and complete a fully charging cycle in default mode without host control. The whole charging cycle includes three phases: pre-charge, constant current charge and constant voltage charge. The device automatically terminates the charge when the charge current is below the preset termination current while in constant voltage phase. Furthermore, when battery voltage goes below the recharge threshold, it will automatically start another charging cycle. The SY20743/B/C is compliant with JEITA specification for Li-Ion batteries.

The following safety protection features are integrated: overvoltage and over-current protections, battery temperature sensing, and charging safety timer. The device also integrates a thermal regulation loop, and thermal shutdown comparator to prevent overheating.

The charging status and fault conditions are reported in the CHRG\_STAT register, and the INT output will trigger to notify the host when any fault occurs. The input source status is reported using the PG\_STAT register and the /PG output (SY20743/C).

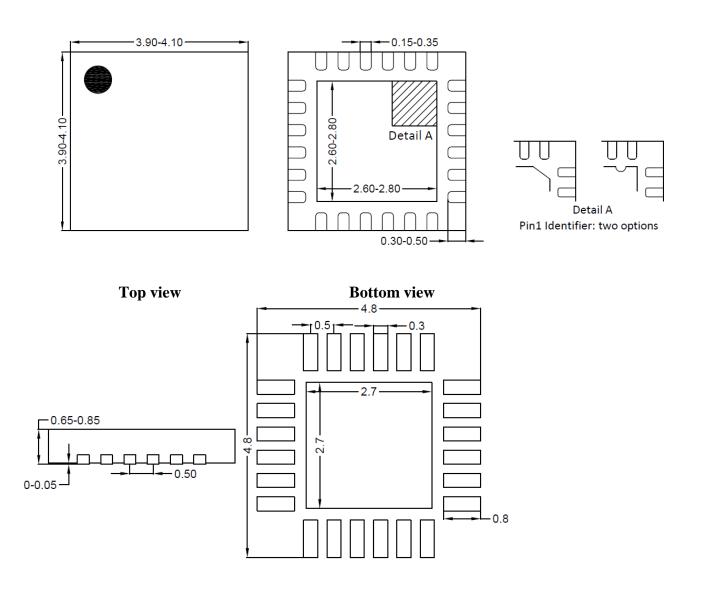

The SY20743/B/C is available in QFN4×4-24 package.

#### **Features**

- High Efficiency 3A 1.5MHz Buck Mode Charger

- 3.9V-13.5V Input Voltage Range

- Programmable IDPM/VDPM thresholds

- Supports USB SDP/DCP/CDP and Non-Standard Adapter Detection (SY20743B)

- 3.856-4.624V Adjustable Charge Voltage

- Supports Narrow VDC Power Path Management

- JEITA Compliant

- ±0.5% Charge Voltage Regulation

- Charge Status Outputs for LEDs or Host Processor

- 1.2A 1.5MHz Boost OTG

- 4.85-5.3V Adjustable OTG Output Voltage

- Selectable OTG Output Current Limit

- ±1.5% Output Regulation in Boost Mode

- Soft-Start supports up to 500µF Capacitive Load

- Constant Current (CC) Limit

- Power path control to support Shipping Mode, Wake Up, and System Reset

- Safety

- Battery temperature sense for charge and boost mode

- Battery charging safety timer

- Thermal regulation and thermal shutdown

- Input/System over-voltage protection

- MOSFET over-current protection

- Low Battery Leakage Current and Support Shipping Mode

## **Applications**

- Smartphones

- Tablets

- Power banks

- Battery operated internet devices.

DS\_SY20743/B/C Rev.1.0 © 2022 Silergy Corp.

1

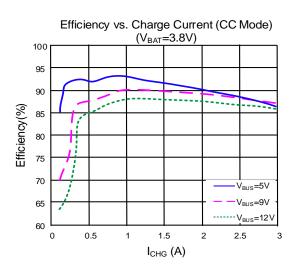

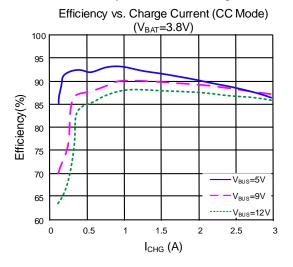

Figure 2. Efficiency vs. Charge Current

## **Ordering Information**

| Ordering<br>Part Number | Package type                               | Top Mark       |

|-------------------------|--------------------------------------------|----------------|

| SY20743QCC              |                                            | CUExyz         |

| SY20743BQCC             | QFN 4×4-24 RoHS Compliant and Halogen Free | <b>DDN</b> xyz |

| SY20743CQCQ             | Kohs Compilant and Halogen Free            | <b>DLM</b> xyz |

$x=year\ code,\ y=week\ code,\ z=lot\ number\ code$

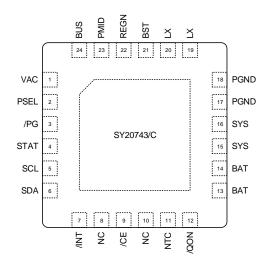

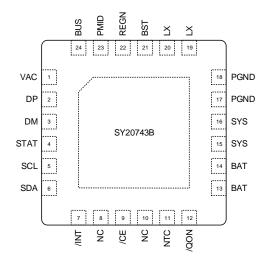

## Pinout (top view)

## **Device Comparison Table**

|               | SY20743   | SY20743B | SY20743C  |

|---------------|-----------|----------|-----------|

| OVP default   | 6.5V      | 6.5V     | 14V       |

| USB detection | PSEL      | DP/DM    | PSEL      |

| Status output | STAT, /PG | STAT     | STAT, /PG |

| Pin Name        | Pin No | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAC             | 1      | Charge input voltage sense. This pin must be connected close to BUS pin                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSEL(SY20743/C) | 2      | Power source selection input. High indicates a USB host source and Low indicates an adapter source. In default mode, set 500mA input current limit by pulling this pin high and set 2.4A input current limit by pulling this pin low.                                                                                                                                                                                                                                                         |

| /PG(SY20743/C)  | 3      | Open drain active low power good indicator. Connect to the pull up rail via $10k\Omega$ resistor. Low indicates a good input source.                                                                                                                                                                                                                                                                                                                                                          |

| DP(SY20743B)    | 2      | USB identification port. USB detection strategy is compliant with BC1.2. SDP, CDP, DCP                                                                                                                                                                                                                                                                                                                                                                                                        |

| DM(SY20743B)    | 3      | and adapter port can be identified according to the detection results thru DP/DM pins.                                                                                                                                                                                                                                                                                                                                                                                                        |

| STAT            | 4      | Open drain charge status output to indicate various charger operation. Connect to the pull up rail via $10k\Omega$ resistor. Low indicates charge in progress. A high level indicates charge complete or charge disabled. When any charge fault condition occurs, STAT pin will blink at 1Hz.  The STAT pin function can be disabled when STAT_DIS bit is set.                                                                                                                                |

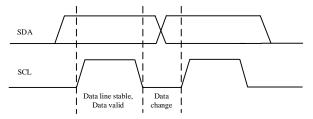

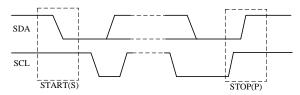

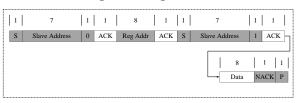

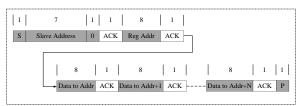

| SCL             | 5      | I <sup>2</sup> C Interface clock. Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDA             | 6      | I <sup>2</sup> C Interface data. Connect SDA to the logic rail through a $10$ kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                    |

| /INT            | 7      | Open-drain interrupt output. Connect the /INT to a logic rail via 10kΩ resistor. The /INT pin sends active low, 256μs pulse to host to report charger device status and fault.                                                                                                                                                                                                                                                                                                                |

| NC              | 8, 10  | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| /CE             | 9      | Active low charge enable pin. Battery charging will be enabled when REG01[4] =1 and /CE pin =Low. /CE pin must be pulled high or low.                                                                                                                                                                                                                                                                                                                                                         |

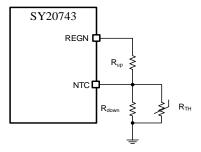

| NTC             | 11     | Temperature sense input. Connect a resistor divider from REGN to NTC to GND to achieve battery thermal protection. Charge will suspend when the NTC pin is out of range. Recommend NTC: 103AT-2 thermistor.                                                                                                                                                                                                                                                                                   |

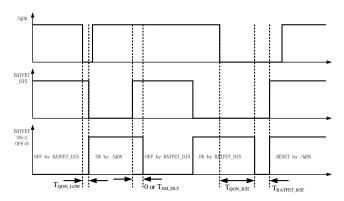

| /QON            | 12     | BATFET enable control in shipping mode and BATFET reset function.  When BATFET is in shipping mode, logic high to low transition on this pin with a minimum of T <sub>QON_LOW</sub> low level will turn on BATFET to exit shipping mode. This pin is internally pulled up to default high logic.  When BUS is not plugged in and BATFET_DIS=0, a logic low of T <sub>QON_RST</sub> will reset SYS (system power) by turning BATFET off for T <sub>BATFET_RST</sub> and then re-enable BATFET. |

| BAT             | 13,14  | Battery connection point to the positive terminal of the battery pack. The internal BATFET is connected between BAT and SYS. Connect a 10μF close to the BAT pin.                                                                                                                                                                                                                                                                                                                             |

| SYS             | 15,16  | System connection point. The internal BATFET is connected between BAT and SYS. Power path management keeps SYS above the minimum system setting, Connect a 20µF ceramic capacitor close to the BAT pin.                                                                                                                                                                                                                                                                                       |

| PGND            | 17,18  | Power ground connection node. Connect directly to the ground connection for the input and output capacitors of the charger.                                                                                                                                                                                                                                                                                                                                                                   |

| LX              | 19,20  | Switching node pin. Connect to external inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BST             | 21     | HSFET driver positive supply. Connect a 47nF bootstrap capacitor from LX to BST.                                                                                                                                                                                                                                                                                                                                                                                                              |

| REGN            | 22     | LSFET driver positive supply. Connect a 4.7µF ceramic capacitor from REGN to analog GND. The capacitor should be placed close to the IC. REGN also serves as bias rail for the external thermistor.                                                                                                                                                                                                                                                                                           |

| PMID            | 23     | Place at least 10μF ceramic capacitor on PMID to PGND, and place it as close as possible to IC.                                                                                                                                                                                                                                                                                                                                                                                               |

| BUS             | 24     | Charger power input pin. Place a 1μF ceramic capacitor from BUS to PGND, and place it as close as possible to IC.                                                                                                                                                                                                                                                                                                                                                                             |

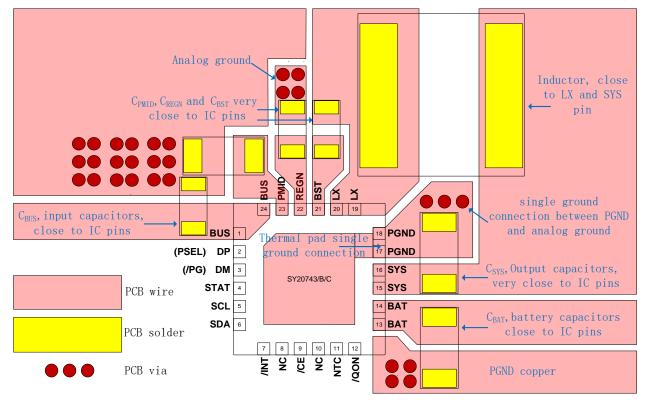

| Exposed pad     | -      | Exposed pad used for heat dissipation. Always connect this pad to the GND plane using multiple vias.                                                                                                                                                                                                                                                                                                                                                                                          |

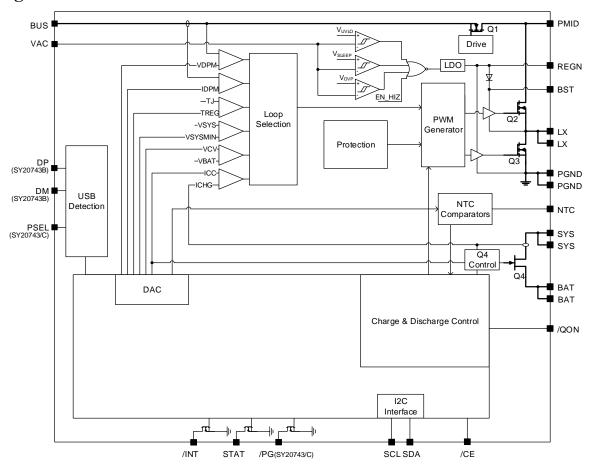

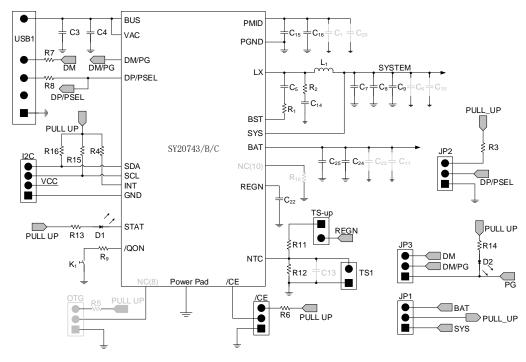

## **Block Diagram**

Figure 3. Block Diagram

| Absolute Maximum Ratings (1)                                                    | Min  | Max | Unit |

|---------------------------------------------------------------------------------|------|-----|------|

| BUS, VAC, PMID, LX                                                              | -0.3 | 18  | V    |

| BAT, SYS, REGN, PSEL, /PG, DP, DM, STAT, SCL, SDA, /INT, /CE, NTC, /QON, BST-LX | -0.3 | 6   | ] v  |

| Junction Temperature Range                                                      | -40  | 150 |      |

| Operating Temperature Range                                                     | -40  | 150 | °C   |

| Storage Temperature                                                             | -65  | 150 |      |

| Thermal Information (2)                              | Min | Max  | Unit |

|------------------------------------------------------|-----|------|------|

| $\theta_{JA}$ Junction-to-ambient Thermal Resistance |     | 27.5 | °C/W |

| θ <sub>JC</sub> Junction-to-case Thermal Resistance  |     | 18   | C/W  |

| ESD Susceptibility (3)    | Min | Max  | Unit |

|---------------------------|-----|------|------|

| HBM (Human Body Mode)     |     | 2000 | V    |

| CDM (Charged Device Mode) |     | 200  | V    |

| Recommended Operating Conditions (4)                                            | Min | Max | Unit |

|---------------------------------------------------------------------------------|-----|-----|------|

| BUS, VAC, PMID, LX                                                              | 0   | 16  | W    |

| BAT, SYS, REGN, PSEL, /PG, DP, DM, STAT, SCL, SDA, /INT, /CE, NTC, /QON, BST-LX | 0   | 5.5 | ľ    |

| Junction Temperature Range                                                      | -40 | 125 | °C   |

| Ambient Temperature Range                                                       | -40 | 85  |      |

## **Electrical Characteristics** (V<sub>BUS\_UVLOZ</sub><V<sub>BUS</sub><V<sub>ACOV</sub> and V<sub>BUS</sub>>V<sub>BAT</sub>+V<sub>SLEEPZ</sub>, T<sub>A</sub>=25°C)

| Parameter                                                             | Syml                     | ool Test Conditions                                                                                                                                             | Min   | Тур        | Max         | Unit   |

|-----------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------------|--------|

| Quiescent Currents                                                    |                          |                                                                                                                                                                 |       |            |             |        |

|                                                                       |                          | V <sub>BUS</sub> <v<sub>BUS_UVLOZ, V<sub>BAT</sub>=4.5 V, leakage between BAT and BUS</v<sub>                                                                   |       |            | 5           | μA     |

| Battery Discharge Current (BAT)                                       | $I_{\mathrm{BAT}}$       | V <sub>BAT</sub> =4.5 V, High-Z Mode, no BUS,<br>BATFET disabled                                                                                                |       | 15         | 25          | μA     |

|                                                                       |                          | V <sub>BAT</sub> =4.5 V, High-Z Mode, no BUS, BATFET enabled                                                                                                    |       | 40         | 55          | μA     |

| Input Supply Current in High-Z Mode                                   | I <sub>BUS HIZ</sub>     | V <sub>BUS</sub> =5V, no battery, High-Z mode enabled                                                                                                           |       | 20         | 35          | μA     |

| input Suppry Current in Fig. 2 Mode                                   | IDUS_IHZ                 | V <sub>BUS</sub> =12V, no battery, High-Z mode enabled                                                                                                          |       | 25         | 50          | μA     |

| Input Supply Current (BUS)                                            | $I_{ m BUS}$             | V <sub>BUS</sub> >V <sub>BUS</sub> _UVLOZ, V <sub>BUS</sub> >V <sub>BAT</sub> , converter not switching                                                         |       | 1.5        | 3           | mA     |

|                                                                       | -500                     | V <sub>BUS</sub> > V <sub>BUS</sub> _ <sub>UVLOZ</sub> , V <sub>BUS</sub> >V <sub>BAT</sub> , converter switching, V <sub>BAT</sub> =3.8V, I <sub>SYS</sub> =0A |       | 3          |             | mA     |

| Battery Discharge Current in Boost<br>Mode                            | I <sub>OTGBOOST</sub>    | V <sub>BAT</sub> =4.2V, Boost mode, I <sub>BUS</sub> =0A, converter switching                                                                                   |       | 3.5        |             | mA     |

| BUS/BAT Power up                                                      | 1                        | T                                                                                                                                                               |       | T          |             |        |

| BUS Operating Range                                                   | V <sub>BUS_OP</sub>      | D: 1 1 20                                                                                                                                                       | 3.9   | 2.2        | 13.5        | V      |

| BUS for Active IC and I <sup>2</sup> C, no Battery                    | V <sub>BUS_UVLOZ</sub>   | Rising value to active I <sup>2</sup> C Falling value                                                                                                           |       | 3.3<br>2.9 | 3.5<br>3.25 | V<br>V |

| Sleep Mode Falling Threshold                                          | V <sub>SLEEP</sub>       | V <sub>BUS</sub> falling, V <sub>BUS</sub> -V <sub>BAT</sub>                                                                                                    | 25    | 65         | 120         | mV     |

| Sleep Mode Rising Threshold                                           | V <sub>SLEEPZ</sub>      | V <sub>BUS</sub> rising, V <sub>BUS</sub> -V <sub>BAT</sub>                                                                                                     | 170   | 250        | 300         | mV     |

| BUS over-Voltage Rising Threshold                                     | V <sub>ACOV</sub>        | V <sub>BUS</sub> rising, REG06[7:6] =00                                                                                                                         | 5.7   | 5.9        | 6.1         | V      |

| BUS over-Voltage Recovery<br>Threshold                                | V <sub>ACOV_RC</sub>     | V <sub>BUS</sub> falling, REG06[7:6] =00                                                                                                                        | 5.5   | 5.7        | 5.9         | V      |

| BUS over-Voltage Rising Threshold                                     | V <sub>ACOV</sub>        | V <sub>BUS</sub> rising, REG06[7:6] =11                                                                                                                         | 13.8  | 14.1       | 14.4        | V      |

| BUS over-Voltage Recovery Threshold                                   | V <sub>ACOV_RC</sub>     | V <sub>BUS</sub> falling, REG06[7:6] =11                                                                                                                        | 13.5  | 13.8       | 14.1        | V      |

| Battery for Active I <sup>2</sup> C, no BUS                           | $V_{BAT\_UVLOZ}$         | V <sub>BAT</sub> rising value to active I <sup>2</sup> C                                                                                                        |       | 2.1        | 2.3         | V      |

| -                                                                     |                          | V <sub>BAT</sub> falling                                                                                                                                        |       | 1.8        | 2.0         | V      |

| Battery Depletion Threshold                                           | V <sub>BAT_DPL</sub>     | V <sub>BAT</sub> falling                                                                                                                                        | 2.15  | 2.3        | 2.5         | V      |

| Battery Depletion Recovery<br>Threshold                               | V <sub>BAT_DPLZ</sub>    | V <sub>BAT</sub> rising                                                                                                                                         | 2.3   | 2.55       | 2.7         | V      |

| Bad Adapter Detection Threshold                                       | V <sub>BUSMIN</sub>      | V <sub>BUS</sub> falling                                                                                                                                        | 3.6   | 3.7        | 3.8         | V      |

| Bad Adapter Detection Hysteresis                                      | VBUSMIN_HYST             | V <sub>BUS</sub> rising                                                                                                                                         |       | 100        |             | mV     |

| Bad Adapter Detection Current Source                                  | IBADSRC                  |                                                                                                                                                                 |       | 30         |             | mA     |

| Bad Source Detection Duration                                         | tbadsrc                  |                                                                                                                                                                 | 1     | 30         | 1           | ms     |

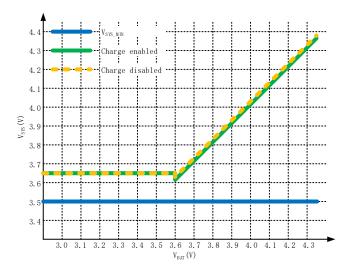

| Power Path Management                                                 | V <sub>SYS_MAX</sub>     | $I_{SYS} = 0A, \ V_{BAT} \gt V_{SYSMIN}, \ BATFET \ off, \\ V_{BAT} \ up \ to \ 4.35V, \ V_{SYS} = V_{BAT} + 50mV$                                              | 4.35  | 4.4        | 4.43        | V      |

| System Regulation Voltage                                             | V <sub>SYS_MIN</sub>     | I <sub>SYS</sub> =0A, V <sub>BAT</sub> <v<sub>SYSMIN=3.5V, BATFET off, V<sub>SYS</sub>=V<sub>BAT</sub>+150mV</v<sub>                                            | 3.55  | 3.65       | 3.75        | V      |

| Internal High-side Reverse Blocking MOSFET on Resistance              | R <sub>ON(RBFET)</sub>   | , , , , , , , , , , , , , , , , , , , ,                                                                                                                         |       | 45         |             | mΩ     |

| Internal High-side Switching MOSFET on Resistance between PMID and LX | Ron(HSFET)               |                                                                                                                                                                 |       | 60         |             | mΩ     |

| Internal low-side Switching MOSFET on Resistance between LX and PGND  | R <sub>ON(LSFET)</sub>   |                                                                                                                                                                 |       | 60         |             | mΩ     |

| BATFET Forward Voltage in Supplement Mode                             | $V_{\mathrm{FWD}}$       | BAT discharge current 10mA                                                                                                                                      |       | 30         |             | mV     |

| Battery Charger                                                       |                          |                                                                                                                                                                 |       |            |             |        |

| Charge Voltage Regulation Accuracy                                    | V <sub>BAT_REG_ACC</sub> | $V_{BAT\_REG} = 4.208V$ and $4.352V$                                                                                                                            | -0.5% |            | 0.5%        |        |

| Fast Charge Current Regulation Accuracy                               | Iichg_reg_acc            | V <sub>BAT</sub> =3.8V, I <sub>CHG</sub> =0.72A or 1.38A                                                                                                        | -5.5% |            | 5.5%        |        |

| Battery LOWV Falling Threshold                                        | V <sub>BATLOWV</sub>     | Fast charge to pre-charge, VBAT falling                                                                                                                         | 2.6   | 2.8        | 2.9         | V      |

**Electrical Characteristics** (V<sub>BUS\_UVLOZ</sub><V<sub>BUS</sub><V<sub>ACOV</sub> and V<sub>BUS</sub>>V<sub>BAT</sub>+V<sub>SLEEPZ</sub>, T<sub>A</sub>=25°C)

| SILERGY                                                                                    |                            |                                                                                                               |               |       |            |      |

|--------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|---------------|-------|------------|------|

| Parameter                                                                                  | Symbol                     | Test Conditions                                                                                               | Min           | Тур   | Max        | Unit |

| Battery LOWV Rising Threshold                                                              | V <sub>BATLOWV_HYST</sub>  | Pre-charge to fast charge, VBAT rising                                                                        | 2.8           | 3.0   | 3.1        | V    |

| Precharge Current Regulation<br>Accuracy                                                   | IPRECHG_ACC                | $V_{BAT} = 2.6V$ , $I_{CHG} = 180mA$                                                                          | -15%          |       | 20%        |      |

| Termination Current Accuracy                                                               | Iterm_acc                  | I <sub>TERM</sub> =180mA, I <sub>CHG_REG</sub> >780mA<br>I <sub>TERM</sub> =60mA, I <sub>CHG REG</sub> ≤780mA | -20%<br>-35%  |       | 20%<br>35% |      |

| Battery Short Voltage                                                                      | V <sub>SHORT</sub>         | V <sub>BAT</sub> falling                                                                                      | 1.9           | 2.0   | 2.1        | V    |

| Battery Short Voltage Hysteresis                                                           | V SHORT<br>VSHORT_HYST     | V <sub>BAT</sub> raining  V <sub>BAT</sub> rising                                                             | 1.9           | 200   | 2.1        | mV   |

| Battery Short Current                                                                      | I <sub>SHORT</sub>         | V <sub>BAT</sub> rising<br>V <sub>BAT</sub> <2.2V                                                             | 55            | 100   | 125        | mA   |

| •                                                                                          |                            | $V_{BAT} < 2.2 \text{ V}$ $V_{BAT} \text{ falling, REG04[0]} = 0$                                             | 75            | 100   | 145        | mV   |

| Recharge Threshold Below V <sub>BAT_REG</sub>                                              | V <sub>RECHG</sub>         | $V_{BAT}$ falling, REG04[0] = 1                                                                               | 160           | 200   | 250        | mV   |

| SYS-BAT MOSFET on Resistance                                                               | Ron_batfet                 |                                                                                                               |               | 17    |            | mΩ   |

| Input Voltage/Current Regulation                                                           | T                          |                                                                                                               | 1             | 1     |            |      |

| Absolute Input Voltage Regulation<br>Accuracy                                              | V <sub>INDPM_REG_ACC</sub> | set absolute VINDPM=4.5V                                                                                      | -1.5%         |       | 1.5%       |      |

| Input Current Limit Range                                                                  | I <sub>INDPM_RANGE</sub>   |                                                                                                               | 100           |       | 3200       | mA   |

|                                                                                            |                            | USB 100mA                                                                                                     | 80            |       | 100        |      |

| USB Input Current Regulation Limit,                                                        | I <sub>USB_DPM</sub>       | USB 500mA                                                                                                     | 440           |       | 500        | mA   |

| BUS=5V, Current Drawn from LX                                                              |                            | USB 900mA                                                                                                     | 750           |       | 900        |      |

| Input Current Regulation Accuracy                                                          | I <sub>ADPT_DPM</sub>      | I <sup>2</sup> C Set input current limit above 900mA                                                          | -15%          | -7%   | 0%         |      |

| BAT over-Voltage Protection                                                                | <u> </u>                   | •                                                                                                             | •             | •     |            |      |

| Battery over-Voltage Threshold                                                             | $V_{BATOVP}$               | V <sub>BAT</sub> rising, as percentage of V <sub>BAT_REG</sub>                                                | 103%          | 104%  | 105%       |      |

| Battery over-Voltage Hysteresis                                                            | V <sub>BATOVP_HYST</sub>   | V <sub>BAT</sub> falling, as percentage of V <sub>BAT_REG</sub>                                               |               | 2%    |            |      |

| BAT Discharge over-Current Protecti                                                        |                            | <u> </u>                                                                                                      |               |       |            |      |

| BATFET Discharge over-Current                                                              |                            |                                                                                                               | 7.5           | 10    | 10.5       |      |

| Threshold                                                                                  | IBATFET_OCP                |                                                                                                               | 7.5           | 10    | 12.5       | A    |

| Thermal Regulation and Thermal Shu                                                         | itdown                     | •                                                                                                             | •             | •     |            |      |

| Junction Temperature Regulation                                                            | T <sub>Junction</sub> REG  | REG05[1] =1                                                                                                   |               | 110   |            | °C   |

| Accuracy Thermal Shutdown Rising                                                           | _                          |                                                                                                               |               |       |            |      |

| Temperature                                                                                | T <sub>TSD</sub>           | Temperature increasing                                                                                        |               | 160   |            | °C   |

| Thermal Shutdown Hysteresis                                                                | T <sub>TSD_HYS</sub>       |                                                                                                               |               | 30    |            | °C   |

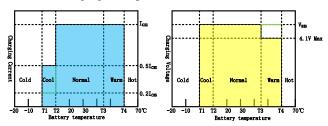

| JEITA Thermistor Comparator                                                                | T                          | 1                                                                                                             | 1             | 1     |            |      |

| T1(0°C) Threshold, Charge Suspended<br>Below this Temp                                     | $V_{T1}$                   | V <sub>NTC</sub> rising, as percentage to V <sub>REGN</sub> , JEITA_ISET=0                                    | 72.75         | 73.25 | 73.75      | %    |

| Charge back to I <sub>CHG</sub> /2 and V <sub>REG</sub> above this Temp                    | V <sub>T1_HYS</sub>        | Hysteresis, V <sub>NTC</sub> falling, JEITA_ISET=0                                                            |               | 1.25  |            | %    |

| T2(10°C) Threshold, Charge back to                                                         | $V_{T2}$                   | V <sub>NTC</sub> rising, as percentage to V <sub>REGN</sub> ,                                                 | 67.75         | 68.25 | 68.75      | %    |

| ICHG/2 and V <sub>REG</sub> below this Temp Charge back to ICHG and V <sub>REG</sub> above |                            | JEITA_ISET=0                                                                                                  | -             |       |            |      |

| this Temp                                                                                  | V <sub>T2_HYS</sub>        | Hysteresis, V <sub>NTC</sub> falling, JEITA_ISET=0                                                            |               | 1.25  |            | %    |

| T3(45°C) Threshold, Charge back to I <sub>CHG</sub> and 4.05V above this Temp              | $V_{T3}$                   | V <sub>NTC</sub> falling, as percentage to V <sub>REGN</sub> ,<br>JEITA_VSET=0                                | 44.25         | 44.75 | 45.25      | %    |

| Charge back to I <sub>CHG</sub> and V <sub>REG</sub> below this Temp                       | V <sub>T3_HYS</sub>        | Hysteresis, V <sub>NTC</sub> rising, JEITA_VSET=0                                                             |               | 1.2   |            | %    |

| T4(60°C) Threshold, Charge                                                                 | $V_{T4}$                   | V <sub>NTC</sub> falling, as percentage to V <sub>REGN</sub> ,                                                | 33.7          | 34.2  | 34.7       | %    |

| Suspended above this Temp Charge back to I <sub>CHG</sub> and 4.05V below                  |                            | JEITA_VSET=0                                                                                                  |               |       |            |      |

| this Temp                                                                                  | V <sub>T4_HYS</sub>        | Hysteresis, V <sub>NTC</sub> rising, JEITA_VSET=0                                                             |               | 1.2   |            | %    |

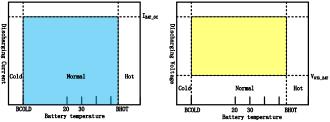

| <b>Boost Mode Thermistor Comparator</b>                                                    |                            |                                                                                                               |               |       |            |      |

| Cold Temperature (-20°C) Threshold 1, NTC pin Voltage Rising Threshold                     | V <sub>BCOLD</sub>         | As Percentage to V <sub>REGN</sub>                                                                            | 79.5          | 80    | 80.5       | %    |

| Falling Hysteresis                                                                         | V <sub>BCOLD_HYS</sub>     |                                                                                                               |               | 1.25  |            | %    |

| Hot Temperature (65°C) Threshold 2,                                                        | V <sub>BHOT</sub>          | As Percentage to V <sub>REGN</sub>                                                                            | 30.6          | 31.1  | 31.6       | %    |

| NTC pin Voltage Falling Threshold                                                          |                            | -                                                                                                             | -             |       |            | 0/-  |

| Rising Hysteresis                                                                          | $V_{BHOT\_HYS}$            |                                                                                                               | 1             | 3     |            | %    |

| Buck Mode Operations USEET Cycle by cycle Current Limit                                    | Twarms                     |                                                                                                               | 1             | -     |            | Α    |

| HSFET Cycle-by-cycle Current Limit                                                         | IHSFET_OCP                 |                                                                                                               | 1200          | 1500  | 1700       | A    |

| PWM Switching Frequency                                                                    | F <sub>SW</sub>            | 117                                                                                                           | 1300          | 1500  | 1700       | kHz  |

|                                                                                            |                            | $_{\text{BUS}}$ < $V_{\text{ACOV}}$ and $V_{\text{BUS}}$ > $V_{\text{BAT}}$ + $V_{\text{SLEEP}}$              | $z$ , $T_A=2$ | 5°C)  |            |      |

| Parameter Symbol                                                                           | <b>Test Conditions</b>     | S Min Typ                                                                                                     | M             | ax    | Un         | it   |

|                                                                                            |                            |                                                                                                               |               |       |            |      |

| ·                                      |                      |                                                                    |       |      |      |     |

|----------------------------------------|----------------------|--------------------------------------------------------------------|-------|------|------|-----|

| <b>Boost Mode Operations</b>           |                      |                                                                    |       |      |      |     |

| PWM Switching Frequency                | Fsw_boost            | V <sub>BAT</sub> =3.2V, V <sub>BUS</sub> =5V, I <sub>BUS</sub> =1A | 1300  | 1500 | 1700 | kHz |

| OTG Output Voltage Range               | Votg_reg             | I <sub>BUS</sub> =0A                                               | 4.85  |      | 5.3  | V   |

| OTG Output Voltage Accuracy            | Votg_reg_acc         | I <sub>BUS</sub> =0A                                               | -1.5% |      | 1.5% |     |

| Battery Voltage Exiting Boost Mode     | V <sub>OTG_BAT</sub> | $REG01[0]) = 0$ , $V_{BAT}$ falling                                | 2.6   | 2.8  | 2.9  | V   |

| Battery Voltage Entering Boost Mode    | Votg_bat_hyst        | $REG01[0]$ ) = 0, $V_{BAT}$ rising                                 | 2.7   | 2.9  | 3.0  | V   |

| Battery Voltage Exiting Boost Mode     | V <sub>OTG_BAT</sub> | REG01[0]) = 1, VBAT falling                                        | 2.4   | 2.5  | 2.6  | V   |

| Battery Voltage Entering Boost Mode    | Votg_bat_hyst        | REG01[0]) = 1, VBAT rising                                         | 2.55  | 2.65 | 2.75 | V   |

| OTG Mode Output Constant Current       | т                    | BOOST_LIM=0.5A                                                     | 0.55  |      | 0.75 | A   |

| Limit                                  | Iotg                 | BOOST_LIM=1.2A                                                     | 1.25  |      | 1.65 | A   |

| OTG over-Voltage Threshold             | $V_{OTG\_OVP}$       | BUS rising edge                                                    | 5.7   | 5.85 | 6    | V   |

| OTG over-Voltage Threshold             |                      | DIIC falliant des                                                  |       | 250  |      | mV  |

| Hysteresis                             | Votg_ovp_hys         | BUS falling edge                                                   |       | 250  |      | mv  |

| REGN LDO                               |                      |                                                                    |       |      |      |     |

| REGN LDO Output Voltage                | V <sub>REGN</sub>    | $V_{BUS} = 10V$ , $I_{REGN} = 40mA$                                |       | 5    |      | V   |

| REGN LDO Output Voltage                |                      | $V_{BUS} = 5V$ , $I_{REGN} = 20mA$                                 |       | 4.8  |      | V   |

| REGN LDO Current Limit                 | Iregn                | $V_{BUS} = 5V$ , $V_{REGN} = 3.8V$                                 | 50    |      |      | mA  |

| /QON Timing                            | •                    |                                                                    |       |      |      |     |

| /QON Low Time to Turn on BATFET        | Toon Low             |                                                                    | 0.9   | 1.1  | 1.3  |     |

| and Exit Ship Mode                     | 1 QON_LOW            |                                                                    | 0.9   | 1.1  | 1.3  | S   |

| /QON Low Time to Reset BATFET          | T <sub>QON_RST</sub> |                                                                    | 8     | 10   | 12   | S   |

| Reset Duration (BATFET off Time)       | TBATFET_RST          |                                                                    | 0.25  | 0.35 | 0.45 | S   |

| Enter Ship Mode Delay                  | tsm_dly              | BATFET_DIS=1, BATFET_DLY=1                                         | 10    | 13   | 15   | S   |

| Logic I/O Pin Characteristics (/CE, PS | SEL, STAT, /PG,      | /INT)                                                              |       |      |      |     |

| Input Low Threshold                    | V <sub>ILOW</sub>    |                                                                    |       |      | 0.4  | V   |

| Input High Threshold                   | V <sub>IHGH</sub>    |                                                                    | 1.3   |      |      | V   |

| Output Low Saturation Voltage          | V <sub>OUT_LOW</sub> |                                                                    |       |      | 0.4  | V   |

| Internal /QON Pull up                  | R <sub>QON</sub>     |                                                                    |       | 220  |      | kΩ  |

| I <sup>2</sup> C Interface (SDA, SCL)  |                      |                                                                    |       |      |      |     |

| Input High Threshold Level             | $V_{IH}$             |                                                                    | 1.3   |      |      | V   |

| Input Low Threshold Level              | $V_{\rm IL}$         |                                                                    |       |      | 0.4  | V   |

| Output Low Threshold Level             | $V_{OL}$             |                                                                    |       |      | 0.4  | V   |

| SCL Clock Frequency                    | fscl                 |                                                                    |       |      | 400  | kHz |

| Digital Clock and Watchdog Timer       |                      |                                                                    |       |      |      |     |

| Watahdag Timoout                       | two                  | REGN LDO disabled, REG05[5:4] =11                                  | 112   | 160  | 208  | S   |

| Watchdog Timeout                       | twdt                 | REGN LDO enabled, REG05[5:4] =11                                   | 136   | 160  | 184  | S   |

|                                        |                      |                                                                    |       |      |      |     |

**Note 1**: Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective four-layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note 3: The device is not guaranteed to function outside its operating conditions.

Note 4: Production testing is performed at 25°C; limits at -40°C to +125°C are guaranteed by design, test or statistical correlation.

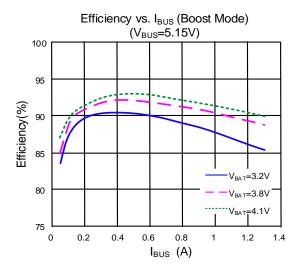

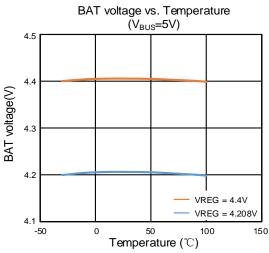

## **Typical Performance Characteristics**

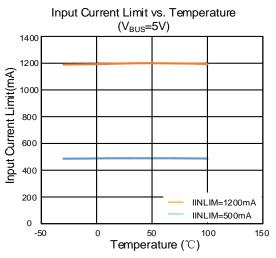

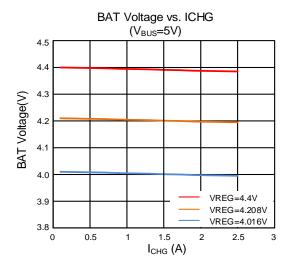

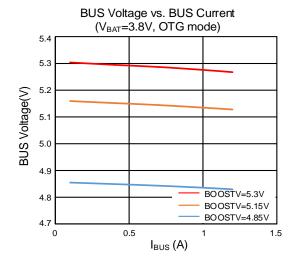

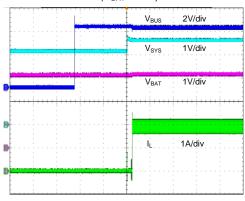

T<sub>A</sub>=25°C, V<sub>BUS</sub>=5V, 1cell battery, unless otherwise specified.

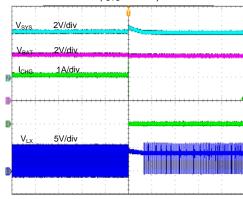

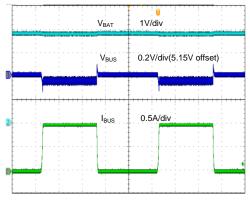

# Adapter Plug-in in Default Mode $(V_{BAT}=3.1V)$

Time (100ms/div)

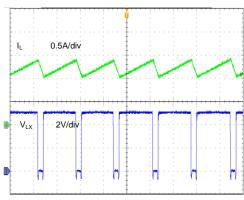

CV Mode Steady State (V<sub>BAT</sub>=4.2V)

Time (400ns/div)

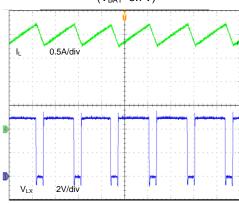

CV Mode Steady State (V<sub>BAT</sub>=3.7V)

Time (400ns/div)

Charge Enable to Disable (I<sub>SYS</sub>=15mA)

Time (800µs/div)

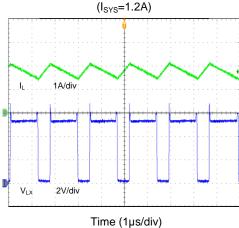

Boost Mode Steady State

**Boost Mode Load Transient**

Time (4ms/div)

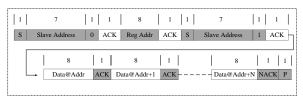

# I<sup>2</sup>C Registers

Address: 6BH **REG00**

| BIT | Name           | POR   | Description                                                                                                                     |

|-----|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 7   | EN_HIZ         | 0     | Enable HIZ Mode:                                                                                                                |

|     |                |       | 0-Disable (Default), 1-Enable                                                                                                   |

| 6:5 | STAT_DIS [1:0] | 00    | Enable STAT pin function:                                                                                                       |

|     |                |       | 00 - Enable STAT pin function (Default)                                                                                         |

|     |                |       | 01 – Reserved                                                                                                                   |

|     |                |       | 10 – Reserved                                                                                                                   |

|     |                |       | 11 - Disable STAT pin function(float)                                                                                           |

| 4:0 | IINLIM [4:0]   | 00100 | Input current limit:                                                                                                            |

|     |                |       | (Actual input current limit by PSEL(SY20743/C) or DP/DM(SY20743B) detection in default mode, and by this register in host mode) |

|     |                |       | IINLIM=100mA+100mA*[IINLIM]                                                                                                     |

|     |                |       | Range:100mA (00000)-3.2A (11111)                                                                                                |

|     |                |       | 00000=100mA                                                                                                                     |

|     |                |       | 00001=200mA                                                                                                                     |

|     |                |       |                                                                                                                                 |

|     |                |       | 00100=500mA (Default)                                                                                                           |

|     |                |       |                                                                                                                                 |

|     |                |       | 11111=3.2A                                                                                                                      |

|     |                |       | IINLIM will be changed after input detection is completed.                                                                      |

|     |                |       | SY20743/C:                                                                                                                      |

|     |                |       | (PSEL=High) 500mA                                                                                                               |

|     |                |       | (PSEL=Low) 2.4A                                                                                                                 |

|     |                |       | SY20743B:                                                                                                                       |

|     |                |       | USB Host SDP=500mA                                                                                                              |

|     |                |       | USB CDP=1.5A                                                                                                                    |

|     |                |       | USB DCP=2.4A                                                                                                                    |

|     |                |       | Host can over-write IINDPM register bits after input source detection is completed.                                             |

| BIT | Name       | POR | Description                                                           |

|-----|------------|-----|-----------------------------------------------------------------------|

| 7   | PFM _DIS   | 0   | PFM mode Disable:                                                     |

|     |            |     | 0- Enable PFM(Default)                                                |

|     |            |     | 1- Disable PFM                                                        |

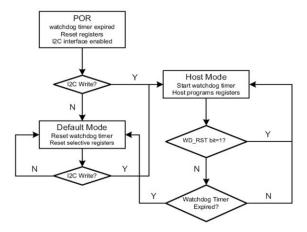

| 6   | WD_RST     | 0   | I <sup>2</sup> C Watchdog Timer Reset:                                |

|     |            |     | 0-Normal (Default)                                                    |

|     |            |     | 1-Reset                                                               |

|     |            |     | Back to 0 after watchdog timer reset.                                 |

| 5   | OTG_CONFIG | 0   | OTG Mode Configuration:                                               |

|     |            |     | 0-OTG Disable (Default)                                               |

|     |            |     | 1-OTG Enable                                                          |

|     |            |     | Note: OTG_CONFIG would over-ride Charge Enable Function in CHG-CONFIG |

| 4   | CHG_CONFIG    | 1   | Charge Enable Configuration:    |

|-----|---------------|-----|---------------------------------|

|     |               |     | 0-Charge Disable                |

|     |               |     | 1-Charge Enable (Default)       |

| 3:1 | SYS_MIN [2:0] | 101 | Minimum System Voltage Limit:   |

|     |               |     | Range:2.6V-3.7V                 |

|     |               |     | 000=2.6V                        |

|     |               |     | 001=2.8V                        |

|     |               |     | 010=3.0V                        |

|     |               |     | 011=3.2V                        |

|     |               |     | 100=3.4V                        |

|     |               |     | 101=3.5V(Default)               |

|     |               |     | 110=3.6V                        |

|     |               |     | 111=3.7V                        |

| 0   | OTG_BAT       | 0   | 0 – 2.8 V BAT falling (Default) |

|     |               |     | 1 – 2.5 V BAT falling           |

#### REG02

| BIT | Name       | POR   | Description                                                           |

|-----|------------|-------|-----------------------------------------------------------------------|

| 7   | BOOST_LIM  | 1     | Boost Mode Current minimum limit:                                     |

|     |            |       | 0 = 0.5  A                                                            |

|     |            |       | 1 = 1.2  A(Default)                                                   |

| 6   | Q1_FULLON  | 0     | RBFET full on for better efficiency in Buck mode:                     |

|     |            |       | $0$ – Use higher Q1 $R_{DS(ON)}$ when programmed IINDPM $\leq 700$ mA |

|     |            |       | (better accuracy)                                                     |

|     |            |       | 1 – Use lower Q1 R <sub>DS(ON)</sub> always (better efficiency)       |

| 5:0 | ICHG [5:0] | 10001 | Fast Charge Current Limit:                                            |

|     |            | 0     | ICHG=[ICHG]*60mA                                                      |

|     |            |       | Range:0mA (000000)-3000mA (110010)                                    |

|     |            |       | 000000=0mA (Disable Charge)                                           |

|     |            |       | 000001=60mA                                                           |

|     |            |       |                                                                       |

|     |            |       | 100010=2040mA (Default)                                               |

|     |            |       |                                                                       |

|     |            |       | 110010~111111=3000mA                                                  |

| BIT | Name          | POR  | Description                 |

|-----|---------------|------|-----------------------------|

| 7:4 | IPRECHG [3:0] | 0010 | Pre-charge Current Limit:   |

|     |               |      | IPRECHG=60mA+[IPRECHG]*60mA |

|     |               |      | Range:60mA-780mA            |

|     |               |      | 0000=60mA                   |

|     |               |      |                             |

|     |               |      | 0010=180mA (Default)        |

|     |               |      |                             |

|     |               |      | 1100~1111=780mA             |

| 3:0 | ITERM [3:0]   | 0010 | Termination Current Limit:  |

|     |               |      | ITERM=60mA+[ITERM]*60mA     |

|     |               |      | Range:60mA-960mA            |

|     |               |      | 0000=60mA                   |

|     |               |      |                             |

|  | 0010=180mA (Default) |

|--|----------------------|

|  | <br>1100=780mA       |

|  | <br>1111=960mA       |

### REG04

| BIT | Name        | POR   | Description                                              |

|-----|-------------|-------|----------------------------------------------------------|

| 7:3 | VREG [4:0]  | 01011 | Charge Voltage Limit:                                    |

|     |             |       | VREG=3.856V+[VREG]*32mV                                  |

|     |             |       | Range:3.856V-4.624V (11000)                              |

|     |             |       | 00000=3.856V                                             |

|     |             |       | 00001=3.888V                                             |

|     |             |       |                                                          |

|     |             |       | 01011=4.208V(Default)                                    |

|     |             |       |                                                          |

|     |             |       | 11000~11111=4.624V                                       |

|     |             |       | Special Value:                                           |

|     |             |       | (01111): 4.352 V                                         |

| 2:1 | TOPOFF_TIME | 00    | The extended charging time after termination enabled and |

|     | R [1:0]     |       | satisfied:                                               |

|     |             |       | 00 – Disabled (Default)                                  |

|     |             |       | 01 – 15 minutes                                          |

|     |             |       | 10 – 30 minutes                                          |

|     |             |       | 11 – 45 minutes                                          |

| 0   | VRECHG      | 0     | Battery Recharge Threshold Offset:                       |

|     |             |       | 0-100mV (Default)                                        |

|     |             |       | 1-200mV                                                  |

| BIT | Name       | POR | Description                              |

|-----|------------|-----|------------------------------------------|

| 7   | EN_TERM    | 1   | Charging Termination Enable:             |

|     |            |     | 0-Disable                                |

|     |            |     | 1-Enable (Default)                       |

| 6   | Reserved   | 0   | Reserved                                 |

| 5:4 | WATCHDOG   | 01  | I <sup>2</sup> C Watchdog Timer Setting: |

|     | [1:0]      |     | 00-Disable timer                         |

|     |            |     | 01-40s(Default)                          |

|     |            |     | 10-80s                                   |

|     |            |     | 11-160s                                  |

| 3   | EN_TIMER   | 1   | Charging Safety Timer Enable:            |

|     |            |     | 0-Disable                                |

|     |            |     | 1-Enable (Default)                       |

| 2   | CHG_TIMER  | 1   | Fast Charge Timer Setting:               |

|     |            |     | 0-5 hours                                |

|     |            |     | 1-10 hours (Default)                     |

| 1   | TREG       | 1   | Thermal Regulation Threshold:            |

|     |            |     | 0-90°C                                   |

|     |            |     | 1-110°C(Default)                         |

| 0   | JEITA_ISET | 1   | JEITA Low Temperature Current Setting    |

| (0℃-10℃) | Percentage with respect to ICHG register REG02[5:0] |

|----------|-----------------------------------------------------|

|          | 0-50%                                               |

|          | 1-20%(Default)                                      |

### REG06

| BIT | Name         | POR  | Description                                |

|-----|--------------|------|--------------------------------------------|

| 7:6 | OVP [1:0]    | 01   | ACOV threshold:                            |

|     |              |      | 00 - 5.5 V                                 |

|     |              |      | 01 – 6.5 V (5-V input) (SY20743/B Default) |

|     |              |      | 10 – 10.5 V (9-V input)                    |

|     |              |      | 11 – 14 V (12-V input) (SY20743C Default)  |

| 5:4 | BOOSTV [1:0] | 10   | Boost Regulation Voltage:                  |

|     |              |      | BOOSTV=4.85V+[BOOSTV]*0.15V                |

|     |              |      | Range: 4.85V-5.3V                          |

|     |              |      | 00=4.85V                                   |

|     |              |      | 01=5.00V                                   |

|     |              |      | 10=5.15V(Default)                          |

|     |              |      | 11=5.30V                                   |

| 3:0 | VINDPM [3:0] | 0110 | Absolute VINDPM Threshold:                 |

|     |              |      | VINDPM=3.9V+[VINDPM]*100mV                 |

|     |              |      | Range:3.9V (0000)-5.4V (1111)              |

|     |              |      | 0000=3.9V                                  |

|     |              |      | 0001=4.0V                                  |

|     |              |      |                                            |

|     |              |      | 0110=4.5V(Default)                         |

|     |              |      |                                            |

|     |              |      | 1111=5.4V                                  |

| BIT | Name        | POR | Description                                                                |

|-----|-------------|-----|----------------------------------------------------------------------------|

| 7   | FORCE_INDET | 0   | Force Start Input Current Limit:                                           |

|     |             |     | 0-Do not force (Default)                                                   |

|     |             |     | 1-Force                                                                    |

|     |             |     | Returns to 0 after input detection is complete.                            |

| 6   | TMR2X_EN    | 1   | Safety Timer Setting during Input DPM and Thermal                          |

|     |             |     | Regulation and JEITA cool:                                                 |

|     |             |     | 0-Safety timer not slowed by 2X during input DPM or thermal                |

|     |             |     | regulation or JEITA cool.                                                  |

|     |             |     | 1-Safety timer slowed by 2X during input DPM or thermal                    |

|     |             |     | regulation or JEITA cool. (Default)                                        |

| 5   | BATFET_DIS  | 0   | Force BATFET Off:                                                          |

|     |             |     | 0-Allow Q4 turn-on (Default)                                               |

|     |             |     | 1-Turn off Q4 with t <sub>SM_DLY</sub> delay time or immediately (REG07[3] |

| 4   | JEITA_VSET  | 0   | JEITA High Temperature Voltage Setting:                                    |

|     | (45°C-60°C) |     | 0-VREG 4.05V (max.) (Default)                                              |

|     |             |     | 1-VREG                                                                     |

| 3   | BATFET_DLY  | 1   | BATFET turn off delay control:                                             |

|     |             |     | 0-Turn off BATFET immediately when BATFET_DIS is set.                      |

|     |             |     | 1-Turn off BATFET with the delay t <sub>SM_DLY</sub> when BATFET_DIS is    |

|     |             |     | set. (Default)                                                             |

| 2   | BATFET_RST_ | 1  | BATFET Reset Enable:                                             |

|-----|-------------|----|------------------------------------------------------------------|

|     | EN          |    | 0-Disable BATFET reset function                                  |

|     |             |    | 1-Enable BATFET reset function (Default)                         |

| 1:0 | VDPM_BAT_T  | 00 | Limit VINDPM to above BAT voltage.                               |

|     | RACK [1:0]  |    | 00 - Disable function (VINDPM set by register) (Default)         |

|     |             |    | 01 - VBAT + 200mV                                                |

|     |             |    | 10 - VBAT + 250mV                                                |

|     |             |    | 11 - VBAT + 300mV                                                |

|     |             |    | When this bit enabled, Actual VINDPM is higher of register value |

|     |             |    | and VBAT + VDPM_BAT_TRACK                                        |

### REG08(Read only)

| BIT | Name       | POR | Description                                                         |

|-----|------------|-----|---------------------------------------------------------------------|

| 7:5 | BUS_STAT   | NA  | BUS Status register:                                                |

|     | [2:0]      |     | SY20743/C:                                                          |

|     |            |     | 000: No input                                                       |

|     |            |     | 001: USB Host SDP                                                   |

|     |            |     | 011: Adapter (2.4A)                                                 |

|     |            |     | 111: OTG                                                            |

|     |            |     | SY20743B:                                                           |

|     |            |     | 000: No input                                                       |

|     |            |     | 001: USB Host SDP: (500mA)                                          |

|     |            |     | 010: USB CDP: (1.5A)                                                |

|     |            |     | 011: USB DCP (2.4 A)                                                |

|     |            |     | 101: Unknown Adapter (500mA)                                        |

|     |            |     | 110: Non-Standard Adapter (1A/2A/2.1A/2.4A)                         |

|     |            |     | 111: OTG                                                            |

|     |            |     | Note: Software current limit is reported in IINLIM register.        |

| 4:3 | CHRG_STAT  | NA  | Charging status:                                                    |

|     | [1:0]      |     | 00-Not Charging                                                     |

|     |            |     | 01-Pre-charge (V <sub>BAT</sub> <v<sub>BATLOWV)</v<sub>             |

|     |            |     | 10-Fast Charging                                                    |

|     |            |     | 11-Charge Termination Done                                          |

| 2   | PG_STAT    | NA  | Power Good Status:                                                  |

|     |            |     | 0-Not Power Good                                                    |

|     |            |     | 1-Power Good                                                        |

| 1   | THERM_STAT | NA  | Thermal Regulation Status:                                          |

|     |            |     | 0-Not in thermal regulation                                         |

|     |            |     | 1- In thermal regulation                                            |

| 0   | VSYS_STAT  | NA  | VSYS Regulation Status:                                             |

|     |            |     | 0-Not in SYSMIN regulation (V <sub>BAT</sub> >V <sub>SYSMIN</sub> ) |

|     |            |     | 1-In SYSMIN regulation (V <sub>BAT</sub> <v<sub>SYSMIN)</v<sub>     |

## REG09(Read only)

| BIT | Name               | POR | Description                                                 |

|-----|--------------------|-----|-------------------------------------------------------------|

| 7   | WATCHDOG_F<br>AULT | NA  | Watchdog Fault status: 0-Normal 1-Watchdog timer expiration |

| 6   | BOOST_FAUL<br>T    | NA  | Boost Mode Fault Status: 0-Normal                           |

|     |            |    | 1-BUS overloaded in OTG, or BUS OVP, or battery is too low              |  |  |

|-----|------------|----|-------------------------------------------------------------------------|--|--|

| 5:4 | CHRG_FAULT | NA | Charge Mode Fault Status:                                               |  |  |

|     | [1:0]      |    | 00-Normal                                                               |  |  |

|     |            |    | 01-Input fault (BUS OVP or V <sub>BAT</sub> <v<sub>BUS&lt;3.8V)</v<sub> |  |  |

|     |            |    | 10-Thermal shutdown                                                     |  |  |

|     |            |    | 11-Charge Safety Timer Expiration                                       |  |  |

| 3   | BAT_FAULT  | NA | Battery Fault Status:                                                   |  |  |

|     |            |    | 0-Normal                                                                |  |  |

|     |            |    | 1-BATOVP                                                                |  |  |

| 2:0 | NTC_FAULT  | NA | NTC Fault Status:                                                       |  |  |

|     | [2:0]      |    | Buck Mode:                                                              |  |  |

|     |            |    | 000-Normal                                                              |  |  |